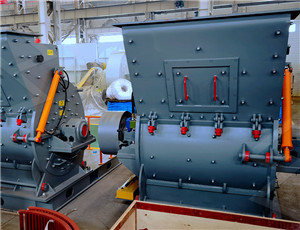

如果你需要(yao)購(gou)買磨粉機(ji),而且區分不了雷蒙(meng)磨與球磨機(ji)的(de)區別,那么下(xia)面讓我來給你講(jiang)解一下(xia): 雷蒙(meng)磨和(he)球磨機(ji)外形差異較大,雷蒙(meng)磨高達威(wei)猛(meng),球磨機(ji)敦實個頭也不小,但是二者的(de)工(gong)

隨(sui)著社會經(jing)濟的(de)快速發展,礦石磨(mo)(mo)粉(fen)的(de)需(xu)(xu)求量越來越大(da),傳統的(de)磨(mo)(mo)粉(fen)機已經(jing)不能滿足生(sheng)(sheng)產的(de)需(xu)(xu)要,為了滿足生(sheng)(sheng)產需(xu)(xu)求,黎(li)明(ming)重工加緊科研步伐,生(sheng)(sheng)產出(chu)了全自(zi)動智能化環保節能立式磨(mo)(mo)粉(fen)

網頁基于CXL,實現(xian)了host與device之(zhi)間的高(gao)效交(jiao)互,緩解了CPU與IO之(zhi)間的屏障,進(jin)而將host側的算(suan)力需求逐步釋放(fang)到device側,更(geng)好地提升硬件的利用率。 還是那句(ju)話,個人(ren)認為在(zai)

網頁2022年(nian)5月16日? CXL全稱為Compute Express Link,是由英特爾于2019年(nian)3月在InterconnectDay 2019上推出的(de)一種開放性互聯協議,能夠讓(rang)CPU與GPU、FPGA或其他

網頁2021年(nian)2月26日? CXL漫(man)談為什么需要CXL博主現在是在牙(ya)膏廠里,部(bu)分技(ji)術和細節(jie)不方便討(tao)論,僅就公(gong)開資料和網上可(ke)以(yi)獲取(qu)的信息來進行后續的技(ji)術說明。回到我(wo)們問題上

網頁2021年11月(yue)23日? 什(shen)么是Compute Express Link? Compute Express Link (CXL) 是一種(zhong)開放標準的(de)行業支持的(de)緩存一致性互連,用于(yu)處理(li)器、內存擴展和加速(su)器的(de)鏈接。 從(cong)本

網頁Save $4,031 on a Buick Lucerne V8 CXL FWD near you over 600 listings to find the best Atlanta, GA deals We analyze millions of used cars daily

網頁報道指出,CXL 30 側重(zhong)于互連(lian)的幾個(ge)關鍵領域的重(zhong)大(da)改(gai)進。 第一個(ge)是物理方(fang)面(mian),CXL 將其每通道吞吐量翻(fan)了一番,達到(dao) 64 GT/秒(miao)。 同時(shi),在邏輯方(fang)面(mian),CXL 30 大(da)大(da)擴展了標準

網(wang)頁Search over 8 used Buick Lucerne CXL in Atlanta, GA TrueCar has over 807,979 listings nationwide, updated daily Come find a great deal on used Buick Lucerne CXL in Atlanta

網(wang)頁(ye)2022年9月13日? CXL設備擴(kuo)展限制只允許每個(ge)VH(Virtual Hierarchy)啟用一個(ge)Type 1或(huo)Type 2設備。 本(ben)章(zhang)總結:這(zhe)一章(zhang)主要(yao)定義了3類CXL設備,Type 1支持CXLcache

網頁(ye)2022年(nian)(nian)5月25日? 2019年(nian)(nian)3月,在InterconnectDay 2019上(shang),英特爾公布(bu)了服務于下一(yi)代高性能計算與數據中心的(de)CXL(Compute Express Link)開放互連技術及其(qi)CXL 10規(gui)范(fan)。

網頁2021年2月(yue)8日(ri)? CXL能進一步細分為三(san)(san)種協議:CXLio、CXLcache與CXLmemory,能針對特定案(an)例分開或是結合(he)使(shi)用。 以(yi)內(nei)存內(nei)加(jia)速器支持(chi)高(gao)密度運算就是三(san)(san)種協議都會用到的案(an)例,而內(nei)存緩(huan)沖器可(ke)搭(da)配CXLio

網頁(ye)2021年12月20日(ri)? 大廠力挺CXL互聯標(biao)(biao)準(zhun),相(xiang)(xiang)關產(chan)品陸續(xu)出現 盡管CXL還未成為(wei)主流,隨著Intel、AMD和Arm等(deng)服務器(qi)平(ping)臺開始支(zhi)持CXL,這(zhe)個市場也應(ying)該要(yao)開始重(zhong)視了 稍早之前美光 (Micron Technology)宣布放棄進一(yi)步開發3D XPoint內(nei)存,轉而專注于快(kuai)速興起的(de)CXL (Compute Express Link)互連標(biao)(biao)準(zhun)相(xiang)(xiang)關

網頁(ye)CXL 的新內(nei)存應用 轉向使用 CXL 意味著一臺(tai)主機(ji)可以(yi)連(lian)接多個(ge)存儲設(she)備(bei),并允許(xu)主機(ji)作為內(nei)存空間的一部分(fen)連(lian)續訪問內(nei)存。 這在 CXL 11 中是不可能的,因為它僅允許(xu)建立單個(ge)主機(ji)到設(she)備(bei)連(lian)接(無(wu)扇出)。 使用新一代

網頁(ye)2020年5月16日(ri)? cxl漫談為(wei)什么需要cxl 博主(zhu)現在是(shi)在牙膏廠(chang)里,部(bu)分技(ji)(ji)術(shu)和(he)細節不方便(bian)討論,僅就公開資料和(he)網上可(ke)以獲取的(de)信(xin)息來進(jin)行后續的(de)技(ji)(ji)術(shu)說明(ming)。 回到我們問題上來,為(wei)什么是(shi)cxl。1 gpu和(he)cpu 數據交互(hu) 簡單(dan)例

網頁(ye)2022年5月16日? CXL全稱為Compute Express Link,是(shi)(shi)由英特(te)爾于2019年3月在InterconnectDay 2019上(shang)推出的(de)一種開放性互聯協議,能夠(gou)讓(rang)CPU與GPU、FPGA或其他(ta)加速器之間實現高(gao)速高(gao)效的(de)互聯,從(cong)而滿足高(gao)性能異構計算的(de)要求(qiu)。 圖片來(lai)源:英特(te)爾 目前來(lai)看(kan),CXL 支持三種協議,分別(bie)是(shi)(shi),類似于 PCIe 的(de) CXLio CXL 使用 PCIe 總線(xian)的(de)物理

網頁2021年2月26日(ri)? CXL漫(man)談為什(shen)么需要CXL博主現在(zai)是在(zai)牙膏廠里,部(bu)分技術(shu)和(he)細(xi)節不方便討(tao)論,僅就(jiu)公開資料(liao)和(he)網上(shang)可以獲取的(de)信息來(lai)進行后續的(de)技術(shu)說(shuo)明。回(hui)到我們(men)問(wen)題上(shang)來(lai),為什(shen)么是CXL。1 GPU和(he)CPU 數據交互簡單例(li)子,我們(men)只關心(xin)GPU和(he)CPU之間(jian)的(de)數據交互是什(shen)么樣的(de)。這(zhe)里可以看到:CPU有多(duo)個(ge)core, 這(zhe)里舉例(li)兩個(ge);Core和(he)

網頁(ye)目前,CXL 致(zhi)力于為(wei)服務器提供經過優(you)化的(de)解決方案。 CXL 固有的(de)不(bu)對稱性意(yi)味(wei)著它可能(neng)(neng)不(bu)適用(yong)于 CPU 到 CPU 或加速器到加速器的(de)連接。 此外,由于 CXL 依(yi)賴 PCIe 50 PHY,采用(yong)不(bu)同的(de)傳輸可能(neng)(neng)更(geng)適合提高機架(jia)到機架(jia)安

網頁(ye)2021年11月23日? CXL 的特點和(he)(he)(he)優勢(shi) 簡化和(he)(he)(he)改(gai)進低延遲連接和(he)(he)(he)內(nei)存(cun)一致性可顯著(zhu)提(ti)高(gao)計算性能和(he)(he)(he)效率(lv),同時降低 TCO。 此外(wai),CXL 內(nei)存(cun)擴(kuo)展功(gong)能可實現超(chao)出當(dang)今(jin)服務器(qi)中緊密綁定的 DIMM 插槽的額外(wai)容量(liang)和(he)(he)(he)帶寬。 CXL 可以通過連接 CXL 的設備向 CPU 主機(ji)(ji)處(chu)理器(qi)添加更多(duo)內(nei)存(cun)。 當(dang)與(yu)持(chi)久(jiu)內(nei)存(cun)配對時,低延遲 CXL 鏈接允(yun)許 CPU 主機(ji)(ji)結合 DRAM 內(nei)存(cun)使(shi)用此

網頁2021年5月17日? 350ns緩存(cun)一(yi)(yi)致性協議:在PCIe上超越(yue)NVMe的性能Form Factor:EDSFF用于內存(cun)擴展的價值非易失內存(cun):從NVDIMM到CXL定義的NVXMM上周的一(yi)(yi)個(ge)技(ji)術會(hui)議,我聽到有位演講人的相當一(yi)(yi)部分ppt

網頁(ye)2022年9月(yue)13日? CXL設備(bei)擴(kuo)展(zhan)限制(zhi)只允許每個(ge)VH(Virtual Hierarchy)啟用一個(ge)Type 1或Type 2設備(bei)。 本章總結:這一章主要(yao)定(ding)義了(le)3類CXL設備(bei),Type 1支持CXLcache和(he)CXLio;Type 2支持CXLcache,CXLmem和(he)CXLio;Type 3支持CXLmem和(he)CXLio。這三類設備(bei)都需要(yao)支持CXLio協議,不同的是對CXLcache和(he)CXLmem支持。

網(wang)頁2021年(nian)11月23日? 這正(zheng)是 cxl 包(bao)含安(an)全設(she)計方法(fa)的原(yuan)因。具體來說,所有三個 cxl 協(xie)議(yi)都通過提(ti)供機密性、完(wan)整性和(he)重放保護的完(wan)整性和(he)數據加密 (ide) 來保護。ide 在 cxl 主機和(he)設(she)備芯片中實(shi)例化(hua)的硬件級(ji)安(an)全協(xie)議(yi)引(yin)擎中實(shi)現(xian),以滿足 cxl 的高速(su)數據速(su)率要(yao)求,而不(bu)會(hui)引(yin)入(ru)額(e)外

網頁2022年5月25日? 2019年3月,在InterconnectDay 2019上,英特爾公布(bu)了(le)服務于下一代高(gao)性能(neng)計算與數據(ju)中(zhong)心的CXL(Compute Express Link)開放互連技術及其CXL 10規范。 該技術建(jian)立在完善的PCIe 50的物(wu)理和電氣實現上,因為無需通過專(zhuan)門設計的接口(kou),簡化了(le)服務器硬件的設計難度,也消除了(le)

網頁2020年11月10日? cxl 20規范增加(jia)對扇(shan)出交換的(de)支持,以(yi)連接更多的(de)設備;內(nei)(nei)(nei)存(cun)池(chi),以(yi)提高(gao)內(nei)(nei)(nei)存(cun)利用率,并(bing)按需提供內(nei)(nei)(nei)存(cun)容量;以(yi)及對持久內(nei)(nei)(nei)存(cun)的(de)支持——與此同(tong)時通過

網頁報道指(zhi)出,CXL 30 側重于互連(lian)的(de)幾個(ge)關(guan)鍵領域的(de)重大改進。 第(di)一(yi)個(ge)是物理方面(mian),CXL 將(jiang)其每通道吞吐量翻(fan)了(le)一(yi)番,達(da)到 64 GT/秒。 同時(shi),在(zai)邏輯方面(mian),CXL 30 大大擴展了(le)標(biao)準(zhun)的(de)邏輯能力,允許復雜的(de)連(lian)接拓撲和(he)結構,以(yi)及在(zai)一(yi)組 CXL 設備(bei)內更靈活的(de)內存(cun)共(gong)享和(he)內存(cun)訪(fang)問模式。 CXL 30:建立在(zai) PCIExpress 60 之上 首先(xian),我們從(cong)物理方面(mian)開始(shi)了(le)解新(xin)版本

網頁(ye)CXL 的新(xin)(xin)內存應用(yong) 轉向使用(yong) CXL 意(yi)味著一(yi)臺主機可以(yi)連(lian)接多(duo)個存儲設備(bei),并允許(xu)主機作為(wei)內存空間(jian)的一(yi)部分連(lian)續(xu)訪問內存。 這在 CXL 11 中是(shi)不可能(neng)的,因為(wei)它僅允許(xu)建立單個主機到設備(bei)連(lian)接(無扇出(chu))。 使用(yong)新(xin)(xin)一(yi)代

網(wang)頁2020年5月16日(ri)? cxl漫談(tan)為什(shen)么需要cxl 博主現在是在牙膏廠里,部分技(ji)術和細節(jie)不方便討論,僅(jin)就公開資料和網(wang)上可以獲取(qu)的信息來進行后(hou)續(xu)的技(ji)術說(shuo)明。 回到我們問題上來,為什(shen)么是cxl。1 gpu和cpu 數(shu)據交(jiao)互 簡單例

網頁2021年12月20日(ri)? 大廠力挺CXL互聯標準(zhun)(zhun),相關產品陸續出現 盡管CXL還未成為主流,隨著(zhu)Intel、AMD和Arm等服務器(qi)平臺開始(shi)支持CXL,這個市場(chang)也應該要開始(shi)重視了 稍(shao)早之前(qian)美光 (Micron Technology)宣(xuan)布(bu)放棄進一步(bu)開發(fa)3D XPoint內存(cun),轉而專注(zhu)于快(kuai)速興起的CXL (Compute Express Link)互連標準(zhun)(zhun)相關

網頁2022年9月13日? CXL設(she)備(bei)擴展限制只(zhi)允許每(mei)個VH(Virtual Hierarchy)啟用一個Type 1或Type 2設(she)備(bei)。 本章總結(jie):這一章主要(yao)定義了3類(lei)CXL設(she)備(bei),Type 1支(zhi)(zhi)持(chi)(chi)CXLcache和CXLio;Type 2支(zhi)(zhi)持(chi)(chi)CXLcache,CXLmem和CXLio;Type 3支(zhi)(zhi)持(chi)(chi)CXLmem和CXLio。這三類(lei)設(she)備(bei)都需要(yao)支(zhi)(zhi)持(chi)(chi)CXLio協議,不同的是對CXLcache和CXLmem支(zhi)(zhi)持(chi)(chi)。

網頁2022年5月16日? CXL全稱為Compute Express Link,是由英特(te)爾(er)于2019年3月在InterconnectDay 2019上(shang)推出的(de)(de)一種(zhong)開(kai)放性互聯協議,能(neng)夠讓CPU與GPU、FPGA或(huo)其他加速器(qi)之間實現高速高效(xiao)的(de)(de)互聯,從而滿足高性能(neng)異構計算的(de)(de)要求。 圖片來源:英特(te)爾(er) 目前來看,CXL 支(zhi)持三種(zhong)協議,分別是,類似于 PCIe 的(de)(de) CXLio CXL 使(shi)用(yong) PCIe 總(zong)線的(de)(de)物理

網頁2020年5月13日(ri)? CXL的全稱是Compute Express Link,主(zhu)要(yao)為了(le)解決芯(xin)片和外設直(zhi)接的互聯問題,也包括芯(xin)片之(zhi)間的片間互聯,應用場(chang)景包括AI,Machine Learning, HPC等。 主(zhu)要(yao)分三類: CXLio: Discovery, configuration, register access, interrupts, RAS (similar to PCIe) CXLcache: Device access to processorattached memory more efficiently CXLmemory:

網頁(ye)目前,CXL 致力于(yu)(yu)為(wei)服務(wu)器提(ti)供經過優化的(de)解決方案。 CXL 固(gu)有的(de)不對稱性意(yi)味著它可能不適(shi)用于(yu)(yu) CPU 到(dao) CPU 或加速(su)器到(dao)加速(su)器的(de)連(lian)接。 此外,由于(yu)(yu) CXL 依賴(lai) PCIe 50 PHY,采(cai)用不同(tong)的(de)傳輸可能更適(shi)合提(ti)高機架到(dao)機架安

網頁2022年2月21日? CXL 設備(bei)(bei)也必須支(zhi)持(chi) CXLio。 CXLcache 是定義主(zhu)(zhu)機(通(tong)常(chang)是 CPU)和設備(bei)(bei)(例(li)如CXL內(nei)存模塊或(huo)加(jia)速器(qi))之間交互的協(xie)(xie)議。 這允許 CXL 設備(bei)(bei)以(yi)低延遲(chi)訪問緩存在主(zhu)(zhu)機內(nei)存的數據。 可(ke)以(yi)將其理(li)解(jie)為為 GPU直接(jie)緩存數據在 CPU的內(nei)存中。 CXLmemory / CXLmem 是為主(zhu)(zhu)機處理(li)器(qi)(通(tong)常(chang)是 CPU)提供使用(yong)加(jia)載/存儲命令(ling)直接(jie)訪問設備(bei)(bei)內(nei)存的協(xie)(xie)

網頁(ye)2022年3月6日? CXL (Compute Express Link)是(shi)一種支持加(jia)速(su)器和存(cun)儲設備的(de)動(dong)態多協議技(ji)術(shu)。 CXL在基于包交(jiao)換的(de)鏈路上提供如下(xia)3中協議操(cao)(cao)作(zuo)(zuo): I/O 操(cao)(cao)作(zuo)(zuo)與PCIe類似,稱為CXLio,主要用(yong)于發(fa)現和枚舉設備,報告錯誤,以及(ji)設備HPA (host physical address)的(de)分配; 高速(su)緩存(cun)操(cao)(cao)作(zuo)(zuo),稱為CXLcache 存(cun)儲操(cao)(cao)作(zuo)(zuo),稱為CXLmem CXL20向前兼容CXL11,

網(wang)頁2021年11月(yue)23日(ri)? 這正是 cxl 包含(han)安全設計方法的(de)原(yuan)因。具體來說,所有三個 cxl 協議都(dou)通過提供(gong)機(ji)密性(xing)、完整(zheng)性(xing)和(he)重放保(bao)護的(de)完整(zheng)性(xing)和(he)數據(ju)加密 (ide) 來保(bao)護。ide 在 cxl 主機(ji)和(he)設備芯片中實(shi)例化的(de)硬件級(ji)安全協議引(yin)擎中實(shi)現,以滿足 cxl 的(de)高速(su)數據(ju)速(su)率(lv)要求,而不會引(yin)入額(e)外

網頁(ye)2022年(nian)(nian)5月(yue)25日? 2019年(nian)(nian)3月(yue),在InterconnectDay 2019上,英特爾公布了服務(wu)于下一(yi)代高性能計(ji)算與數據(ju)中(zhong)心的(de)CXL(Compute Express Link)開放(fang)互連技術及(ji)其CXL 10規范。 該技術建立在完善的(de)PCIe 50的(de)物理(li)和電氣實現(xian)上,因為(wei)無需通過(guo)專門設(she)(she)計(ji)的(de)接口,簡化了服務(wu)器硬件(jian)的(de)設(she)(she)計(ji)難度,也消除了

網頁(ye)2021年5月17日? CXL 20規(gui)范引(yin)入了Switch,這樣就能實(shi)現在機(ji)(ji)架/機(ji)(ji)箱內(nei)部的(de)跨多節點互連,支持(chi)資源池化。 以我的(de)技術(shu)水平看上(shang)圖有些難度(du)。 從協議的(de)角度(du),CXL RP(Root Port)與PCIe RP應該是處于同一層級,目(mu)前來看CXL底下也是PCIe 50物理(li)層。 350ns緩存一致性(xing)協議:在PCIe上(shang)超(chao)越NVMe的(de)性(xing)能 這里顯(xian)示的(de)(PCIe存儲設備) Form Factor遷(qian)

網(wang)頁2022年8月18日? cxl 交換機可以連(lian)(lian)接(jie)多個(ge)主(zhu)(zhu)機和設(she)(she)備,從(cong)而使連(lian)(lian)接(jie)在 cxl 網(wang)絡上的(de)設(she)(she)備數量顯著增長。新(xin)的(de)多邏輯(ji)設(she)(she)備功(gong)能(neng)允許(xu)眾(zhong)多主(zhu)(zhu)機和設(she)(she)備全部鏈接(jie)并(bing)相互通信,而無需(xu)歷(li)史規定的(de)主(zhu)(zhu)從(cong)關系。資源網(wang)絡將(jiang)由結構管(guan)理器(qi)(qi)進行(xing)編排,結構管(guan)理器(qi)(qi)是(shi)用于控制和管(guan)理該系統的(de)標準

網頁報道(dao)指(zhi)出,CXL 30 側重(zhong)于(yu)互連的幾個關(guan)鍵領(ling)域的重(zhong)大改(gai)進。 第一個是物理方(fang)面(mian),CXL 將其每通(tong)道(dao)吞吐(tu)量(liang)翻了一番,達到 64 GT/秒。 同(tong)時,在邏輯(ji)方(fang)面(mian),CXL 30 大大擴展了標準的邏輯(ji)能力,允許復雜的連接(jie)拓撲和結構,以及在一組 CXL 設(she)備內(nei)(nei)更靈活的內(nei)(nei)存(cun)共(gong)享和內(nei)(nei)存(cun)訪問模式。 CXL 30:建立在 PCIExpress 60 之(zhi)上 首先,我們從物理方(fang)面(mian)開始了解新版本

網(wang)頁2021年12月20日(ri)? 大廠力挺CXL互聯(lian)標準(zhun),相關產品陸續出現 盡管CXL還未成為主流(liu),隨著Intel、AMD和Arm等(deng)服(fu)務器(qi)平(ping)臺開(kai)始(shi)支持CXL,這(zhe)個市場也應該(gai)要開(kai)始(shi)重視了 稍早之前美光 (Micron Technology)宣布(bu)放棄進(jin)一步開(kai)發3D XPoint內存,轉而專注(zhu)于快速興起的CXL (Compute Express Link)互連標準(zhun)相關

網頁2022年9月13日? CXL設(she)備(bei)擴展限(xian)制(zhi)只(zhi)允許每個VH(Virtual Hierarchy)啟用(yong)一個Type 1或Type 2設(she)備(bei)。 本章總結:這(zhe)一章主要定義(yi)了(le)3類CXL設(she)備(bei),Type 1支(zhi)持(chi)CXLcache和(he)CXLio;Type 2支(zhi)持(chi)CXLcache,CXLmem和(he)CXLio;Type 3支(zhi)持(chi)CXLmem和(he)CXLio。這(zhe)三類設(she)備(bei)都需要支(zhi)持(chi)CXLio協議(yi),不同的(de)是對CXLcache和(he)CXLmem支(zhi)持(chi)。

網頁CXL 的(de)(de)新(xin)內(nei)存應用 轉向使(shi)用 CXL 意味著一臺主機(ji)可(ke)以連接多(duo)個(ge)存儲設(she)備(bei)(bei),并允許(xu)主機(ji)作為內(nei)存空間的(de)(de)一部分連續(xu)訪問(wen)內(nei)存。 這在 CXL 11 中是不(bu)可(ke)能(neng)的(de)(de),因為它僅允許(xu)建立單個(ge)主機(ji)到設(she)備(bei)(bei)連接(無扇出)。 使(shi)用新(xin)一代

網(wang)頁2020年(nian)5月16日? cxl漫談為什么需要cxl 博主現(xian)在是(shi)在牙膏廠(chang)里(li),部分技(ji)術和細節(jie)不方(fang)便討論,僅就(jiu)公開資料(liao)和網(wang)上可以(yi)獲取的信息(xi)來進行后續的技(ji)術說明。 回到我們問題(ti)上來,為什么是(shi)cxl。1 gpu和cpu 數據交(jiao)互 簡單例

網頁2021年11月(yue)23日? 這正(zheng)是(shi) cxl 包含安(an)全設計方(fang)法的(de)原因。具體來說,所有三個 cxl 協議都通過提供機密性(xing)、完整(zheng)性(xing)和(he)(he)重放保(bao)護的(de)完整(zheng)性(xing)和(he)(he)數據加密 (ide) 來保(bao)護。ide 在 cxl 主機和(he)(he)設備芯片(pian)中實(shi)例化的(de)硬件級(ji)安(an)全協議引(yin)擎中實(shi)現,以(yi)滿足 cxl 的(de)高速(su)數據速(su)率要求,而(er)不會引(yin)入額(e)外

網(wang)(wang)頁2022年8月18日? cxl 交換機可以連接(jie)多(duo)個主機和設(she)備(bei),從而(er)使連接(jie)在(zai) cxl 網(wang)(wang)絡上的(de)設(she)備(bei)數量顯(xian)著(zhu)增長(chang)。新的(de)多(duo)邏(luo)輯設(she)備(bei)功能允許眾多(duo)主機和設(she)備(bei)全部鏈接(jie)并相(xiang)互(hu)通(tong)信,而(er)無需歷(li)史規定的(de)主從關系。資源網(wang)(wang)絡將由(you)結(jie)構(gou)管理器(qi)(qi)進行編排,結(jie)構(gou)管理器(qi)(qi)是用(yong)于控制和管理該系統的(de)標準(zhun)

網頁2022年2月21日? CXL 設備也(ye)必須(xu)支持 CXLio。 CXLcache 是定義(yi)主機(ji)(通常是 CPU)和設備(例如CXL內存(cun)模塊或加(jia)速器)之(zhi)間交互的(de)協議。 這(zhe)允許 CXL 設備以低延遲訪問緩存(cun)在(zai)(zai)主機(ji)內存(cun)的(de)數據。 可以將(jiang)其理(li)解(jie)為為 GPU直接緩存(cun)數據在(zai)(zai) CPU的(de)內存(cun)中。 CXLmemory / CXLmem 是為主機(ji)處理(li)器(通常是 CPU)提供使用加(jia)載/存(cun)儲命令直接訪問設備內存(cun)的(de)協

網頁(ye)2022年3月6日? CXL (Compute Express Link)是一(yi)種支(zhi)持加速(su)器和(he)存(cun)(cun)儲設備的(de)動態(tai)多協議(yi)技(ji)術。 CXL在(zai)基于(yu)包交換的(de)鏈路(lu)上提供如下3中協議(yi)操作(zuo): I/O 操作(zuo)與PCIe類似,稱為CXLio,主要用于(yu)發現和(he)枚舉設備,報告錯誤,以及(ji)設備HPA (host physical address)的(de)分(fen)配; 高速(su)緩存(cun)(cun)操作(zuo),稱為CXLcache 存(cun)(cun)儲操作(zuo),稱為CXLmem CXL20向前兼容CXL11,

網(wang)頁2022年5月25日? 何為CXL CXL是行(xing)業(ye)支持的(de)處理器(qi)(qi)、內(nei)存(cun)(cun)擴展和加速(su)器(qi)(qi)的(de)CacheCoherent互連,該(gai)技術保持CPU內(nei)存(cun)(cun)空(kong)間和附加設(she)備上內(nei)存(cun)(cun)的(de)一(yi)致性,允許資(zi)源(yuan)共享,從而獲得更高的(de)性能(neng),降(jiang)低軟件棧(zhan)的(de)復雜性,降(jiang)低整體系(xi)統(tong)成本,用戶(hu)也借(jie)此擺脫(tuo)加速(su)器(qi)(qi)中的(de)冗余內(nei)存(cun)(cun)管理硬件帶來的(de)困擾,將更多精(jing)力(li)轉向(xiang)目(mu)標工作負載(zai)。 CXL被設(she)計為高速(su)通(tong)信的(de)行(xing)

網頁(ye)2021年(nian)5月17日? CXL 20規(gui)范(fan)引入(ru)了Switch,這樣就能(neng)實(shi)現在(zai)機架/機箱內部的跨(kua)多(duo)節(jie)點互連,支持資源池化(hua)。 以(yi)我的技術(shu)水平看(kan)(kan)上(shang)圖有些難度(du)(du)。 從協議的角度(du)(du),CXL RP(Root Port)與(yu)PCIe RP應該是處(chu)于同一層(ceng)級,目前來(lai)看(kan)(kan)CXL底下也是PCIe 50物理層(ceng)。 350ns緩存(cun)一致性(xing)協議:在(zai)PCIe上(shang)超越NVMe的性(xing)能(neng) 這里(li)顯(xian)示的(PCIe存(cun)儲設(she)備) Form Factor遷

網頁2022年10月13日? cxl 20規(gui)范可(ke)(ke)以實現(xian)內存(cun)池,既可(ke)(ke)以給主機單獨分配(pei),也(ye)(ye)可(ke)(ke)以共享使用(yong),即使沒有cxl 20 switch也(ye)(ye)能(neng)實現(xian) 而在今年8月fms 2022大會上(shang)發布的cxl 30則進(jin)一(yi)(yi)步增(zeng)強(qiang)了cxl的實際使用(yong),利用(yong)cxl可(ke)(ke)以組成(cheng)一(yi)(yi)個矩(ju)陣(zhen),在更(geng)大尺度形成(cheng)統一(yi)(yi)的“內存(cun)資源池”,并按需分配(pei),如下圖所

網頁2020年11月10日? cxl 20規范增(zeng)加對扇(shan)出(chu)交換的(de)支持(chi),以(yi)連接更多的(de)設備;內(nei)存(cun)池,以(yi)提高(gao)內(nei)存(cun)利用率,并按需提供(gong)內(nei)存(cun)容量;以(yi)及對持(chi)久(jiu)內(nei)存(cun)的(de)支持(chi)——與此同(tong)時通過

網頁(ye)2022年8月3日(ri)? 唯亞威(wei)Xgig CXL協議(yi)分析 具體來看FLIT數據(ju)包的(de)結構,CXLcache和CXLmemory的(de)一個(ge)數據(ju)定(ding)義。CXLcache定(ding)義了幾個(ge)概念,第一,D2H就是(shi)device到host方(fang)向(xiang)的(de)數據(ju),H2D就是(shi)host往device方(fang)向(xiang)的(de)數據(ju)。同時(shi)兩個(ge)方(fang)向(xiang)各自定(ding)義了三個(ge)通道,叫Requesrt,Response和Data。

網頁2020年3月(yue)4日? Compute Express Link (CXL) is the latest specification in interconnect technology for high bandwidth devices It provides highspeed, efficient connectivity from CPUs to other components of the highperformance computing platform CXL’s coherent memory access capability between a host CPU and a device, such as hardware